## Filière Systèmes Industriels

Orientation Infotronics

# Travail de bachelor Diplôme 2022

**Xavier Clivaz**

FPGA CI/CD

Professeur

Prof. Silvan Zahno

Expert

Jérome Corre

Date de la remise du rapport

19.08.2022

### Données du travail de diplôme Aufgabenstellung der Bachelorarbeit

FO 1.2.02.07.EB che/31/05/2021

| Filière / Studiengang<br>SYND                                                                     | Année académique <i>I Studienjahr</i> 2021-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | No TB / Nr. BA<br>IT/2022/73                                                                                                                                        |

|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mandant / Auftraggeber  ☑ HES—SO Valais ☐ Industrie ☐ Etablissement partenaire Partnerinstitution | Etudiant / Student Xavier Clivaz  Professeur / Dozent Silvan Zahno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Lieu d'exécution / Ausführungsort  HES—SO Valais Industrie Etablissement partenaire Partnerinstitution                                                              |

| Travail confidentiel / vertrauliche Arbeit ☐ oui / ja      ☐ non / nein                           | Expert / Experte (données complètes)  Jérome Corre - jecensuisse@gma  3D2Cut, Route de Sion 29, 3960 S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                     |

| Titre / Titel FPGA CI/CD - Au                                                                     | tomated hardware develo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | pment toolchain                                                                                                                                                     |

| Description / Beschreibung                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                     |

| developement. It allows to automatically                                                          | verify and deploy a software project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | widely used in the industry for software<br>tts. HEI has a fully working Gitlab Server<br>t as widely adopted for FPGA/Hardware                                     |

|                                                                                                   | automatically generate VHDL code ream generation workflow (CD).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FPGA workflows (CI/CD), and implement from Spinal, run VHDL simulation and to of the FPGA-EBS Board.                                                                |

| as manifests  — Implementation of a CD-workflow for                                               | C capable of running the developed in to start the appropriate CI/CD work automatic VHDL/Verilog generation automatic VHDL testbench simulation automatic generation of Xilinx bitstraware based code evaluation with the company of the code of the c | offlows only if necessary  from a HDL-Designer project  In and analysis with waveform files stored  eam file as manifest  the help of a gitlabrunner and a Digilent |

| Signature ou visa / Unterschrift oder Visu                                                        | um Délais / Termi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ne                                                                                                                                                                  |

| Responsable de l'orientation / Leiter der Vertiefungsrichtung:                                    | 16.05.2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | thème / Ausgabe des Auftrags:                                                                                                                                       |

|                                                                                                   | Présentation ii <b>20-21.06.2022</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ntermédiaire / Zwischenpräsentation:                                                                                                                                |

|                                                                                                   | Remise du rap<br>19.08.22, 12:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | pport final / Abgabe des Schlussberichts:                                                                                                                           |

| <sup>1</sup> Etudiant / Student :                                                                 | Expositions / A 24-26.08.2022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Ausstellungen der Diplomarbeiten:                                                                                                                                   |

Défense orale / Mündliche Verfechtung: Semaine/Woche 36 (5-9.09.2022)

Par sa signature, l'étudiant-e s'engage à respecter strictement la directive DI.1.2.02.07 liée au travail de diplôme. Durch seine Unterschrift verpflichtet sich der/die Student/in, sich an die Richtlinie DI.1.2.02.07 der Diplomarbeit zu halten.

#### Travail de diplôme | édition 2022 |

Filière Systèmes industriels

Domaine d'application Infotronics

Professeur responsable Silvan Zahno silvan.zahno@hevs.ch

#### FPGA CI/CD – Chaîne d'outils EDA automatisée

Diplômant/e Xavier Clivaz

#### Objectif du projet

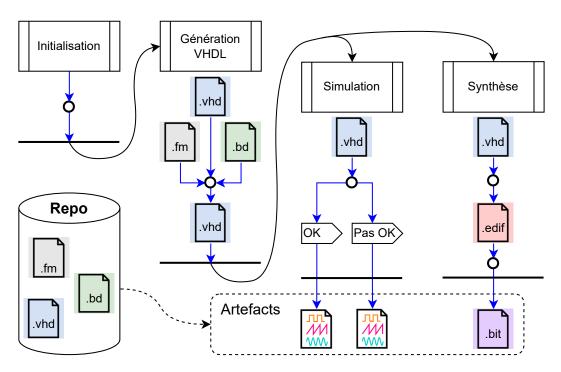

L'objectif de ce travail est de concevoir un pipeline automatisé pour un développement matériel à l'aide de l'outil GitLab-CI et construit à partir de trois processus, la génération de fichiers VHDL, la simulation et la synthèse.

#### Méthodes | Expériences | Résultats

Afin de réaliser un pipeline automatisé, il a dû être adapté sur la plateforme d'hébergement GitLab avec l'outil GitLab-CI s'occupant de l'exécution des processus. Cet outil a été installé sur une machine physique ayant l'environnement Windows. Trois flux de travail ont été réalisés pour la construction du pipeline, la génération de fichiers VHDL, la simulation et la synthèse.

L'approche pour y parvenir consistait à dresser en premier lieu un état de l'art sur les logiciels EDA utilisés au sein du CI/CD. Une vue d'ensemble de toute l'automatisation du pipeline a ensuite été réalisée dans le but d'implémenter le tout plus facilement. En parallèle, l'implémentation a été élaborée processus par processus.

A la fin, une preuve de concept est démontrée. Cette pratique du CI/CD a entièrement pu être réalisée pour un développement matériel. Des tests sur un projet concret ont été effectués pour le prouver.

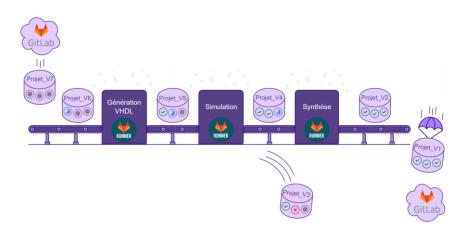

Pipeline automatisé pour développement matériel avec la plateforme GitLab

## Information à propos de ce rapport

#### Information de contact

Auteur: Xavier Clivaz

Etudiant Bachelor HES-SO//Valais Wallis

Suisse

Email: xavierclivaz@hotmail.com

#### Déclaration d'honneur

Signature:

Je, soussigné, Xavier Clivaz, déclare que le travail présenté est le résultat d'un travail personnel. Je certifie que je n'ai pas eu recours au plagiat ou à d'autres formes de fraude. Toutes les sources d'information utilisées et les citations de l'auteur ont été clairement mentionnées.

Lieu, date : 18 août 2022

## Remerciements

Ce travail de bachelor n'a pas été rédigé durant trois mois sans le soutien de plusieurs personnes. Ces contributeurs, qu'ils soient en étroite relation au projet ou bien à l'écart de ce monde numérique, il est l'heure de tous les remercier.

- Je tiens, en premier lieu, à remercier ma famille et singulièrement mes parents, sans qui, je ne pourrais réaliser tous mes voeux. Je peux ainsi, en toute circonstance, m'épanouir pleinement dans ma vie quotidienne. Il s'agit d'une force d'âme transmise qui me permettra toujours d'aller de l'avant malgré les obstacles rencontrés.

- Je remercie secondement mon responsable, M. Silvan Zahno, qui a toujours été à mon entière disposition. Il a su m'apporter ses précieux conseils tout au long du travail afin d'arriver au résultat désiré.

- Je remercie aussi les collaborateurs de la Haute Ecole d'Ingénierie et tout particulièrement M. Axel Amand. Ils ont continuellement été disponibles pour fournir leurs connaissances et leurs avis.

- Je remercie, en dernier lieu, mes camarades de classe pour leur soutien et sans qui, je n'aurais pu me changer les idées durant les courtes pauses de midi.

## Résumé

Ancrée dans l'esprit des développeurs, la gestion de versions ne se présente plus. Cette technique a été complétée par la méthode du DevOps visant à automatiser les processus de développements logiciels à l'aide de l'intégration continue (Continuous Integration) et de la distribution continue (Continuous Delivery). Ayant observé l'optimisation de ces pratiques, la Haute Ecole d'Ingénierie souhaite à présent mettre en oeuvre ces moyens pour des développements matériels.

L'objectif de ce travail est d'implémenter un pipeline automatisé pour un développement matériel, plus particulièrement pour un module de développement FPGA. Ce pipeline doit être adapté sur la plateforme d'hébergement GitLab avec l'outil GitLab-Cl s'occupant de l'exécution des processus. Cet outil doit être installé sur une machine physique ayant l'environnement Windows. Trois flux de travail doivent être réalisés pour la construction du pipeline, la génération de fichiers VHDL, la simulation et la synthèse.

L'approche pour y parvenir consiste à dresser en premier lieu un état de l'art sur les logiciels EDA utilisés au sein du CI/CD. Une vue d'ensemble de toute l'automatisation du pipeline est ensuite réalisée dans le but d'implémenter le tout plus facilement. En parallèle, l'implémentation est élaborée processus par processus.

A la fin, une preuve de concept est démontrée. Cette pratique du CI/CD a entièrement pu être réalisée pour un développement matériel. Des tests sur un projet concret ont été effectués pour le prouver.

Key words: CI, CD, FPGA, EDA

## Table des matières

| Re  | emerciements                                                                                                                                                                       | vii                        |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Ré  | ésumé                                                                                                                                                                              | ix                         |

| Та  | able des matières                                                                                                                                                                  | x                          |

| Lis | ste des figures                                                                                                                                                                    | xii                        |

| Lis | ste des tableaux                                                                                                                                                                   | xiii                       |

| Lis | ste des codes sources                                                                                                                                                              | xiii                       |

| 1   | Introduction  1.1 Problématique                                                                                                                                                    | 1<br>2<br>3<br>4<br>4      |

| 2   | Analyse  2.1 Définitions  2.2 CI/CD pour développement matériel  2.3 Outils de CI  2.4 Génération de fichiers VHDL à partir de HDS  2.5 Simulation  2.6 Synthèse et implémentation | 5<br>6<br>7<br>7<br>8<br>9 |

| 3   | Conception  3.1 GitLab Runner                                                                                                                                                      | 15<br>16<br>20<br>22<br>26 |

| 4   | Implémentation4.1 GitLab Runner4.2 Pipeline4.3 Flux de travail CI4.4 Flux de travail CD                                                                                            | 29<br>30<br>34<br>43<br>51 |

| 5   | Validation         5.1 Tests des différents flux de travail                                                                                                                        | <b>57</b><br>58            |

#### Table des matières

|    | <ul><li>5.2</li><li>5.3</li></ul> | Tests sur carte de développement FPGA                  | 64<br>65                    |

|----|-----------------------------------|--------------------------------------------------------|-----------------------------|

| 6  | Con<br>6.1<br>6.2<br>6.3<br>6.4   | Clusion  Résumé du projet                              | 67<br>67<br>67<br>68<br>68  |

| A  | <b>Doc</b> A.1 A.2                |                                                        | <b>69</b><br>69             |

| В  |                                   | veTcl Installer le programme ActiveTcl                 | <b>73</b> 73                |

| С  | C.1                               | Cloner un répertoire avec un ou plusieurs sous-modules | <b>79</b><br>79<br>82<br>82 |

| D  | Prot                              | cocole de test - Projet chronomètre                    | 83                          |

| Bi | bliog                             | raphie                                                 | 97                          |

| GI | ossaiı                            | re                                                     | 101                         |

| Ac | ronyı                             | mes                                                    | 103                         |

# Table des figures

| 1.1<br>1.2                        | Exemple de gestion de versions avec deux branches                                                                           | 1<br>1 |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------|

| 1.3                               | Illustration d'une automatisation de plusieurs processus                                                                    | 2      |

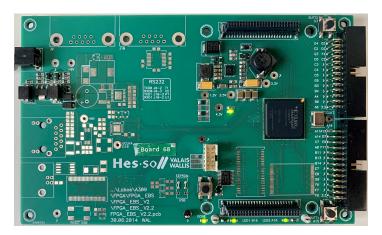

| 1.4                               | Carte de développement FPGA, FPGA-EBS                                                                                       | 3      |

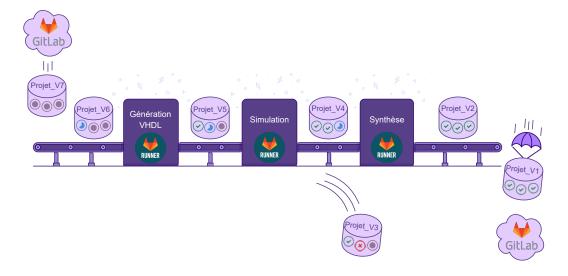

| 1.5                               | Pipeline automatisé avec la plateforme GitLab [1]                                                                           | 3      |

| 2.1                               | Chemin de programmation d'une carte FPGA                                                                                    | 7      |

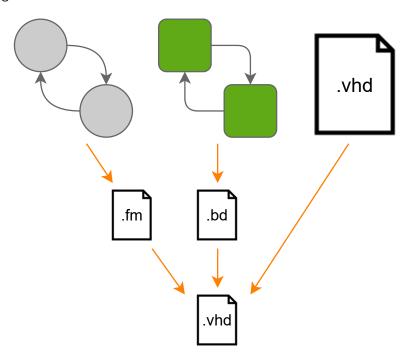

| <ul><li>2.2</li><li>2.3</li></ul> | Arborescence des conversions pour la génération VHDL  Organigrammes montrant la procédure générale de simulation (à gauche) | 9      |

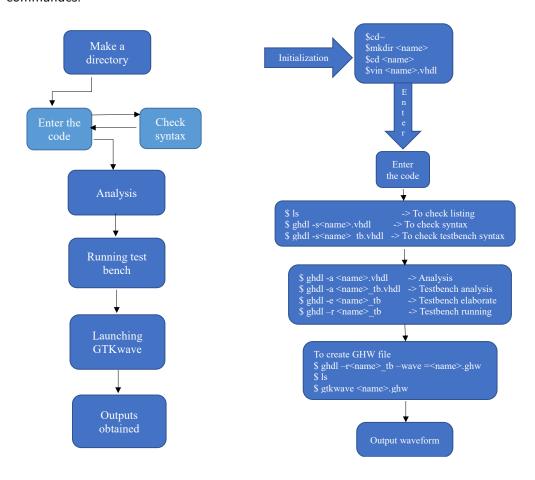

| 2.5                               | et les commandes à utiliser à chaque étape (à droite)                                                                       | 11     |

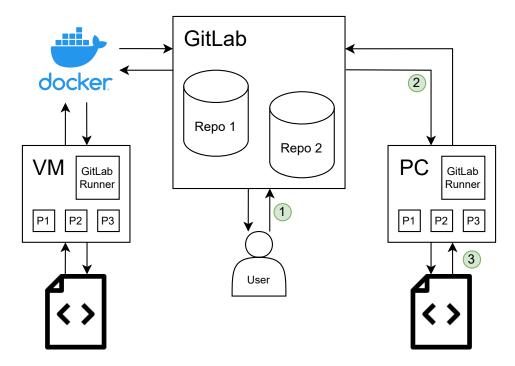

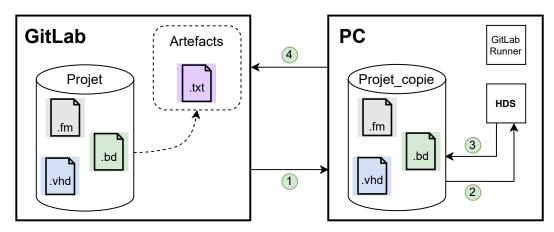

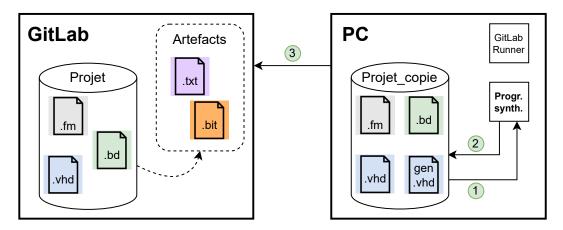

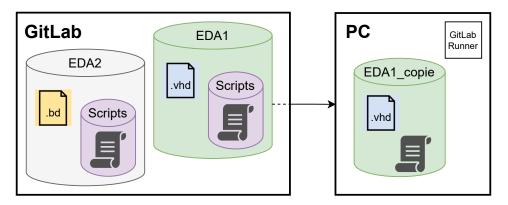

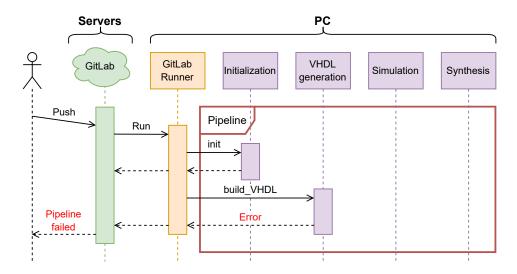

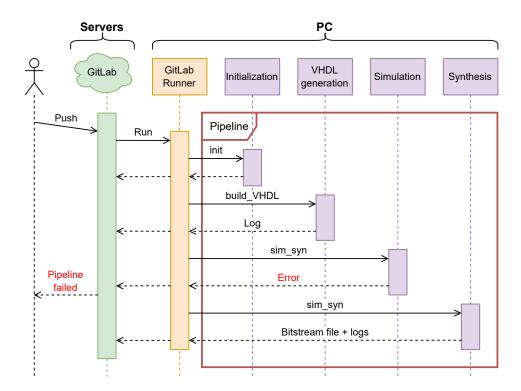

| 3.1                               | Schéma de fonctionnement avec GitLab Runner                                                                                 | 16     |

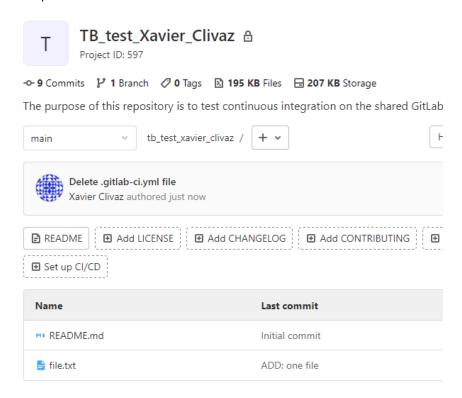

| 3.2                               | Répertoire de test pour le service de GitLab Runner                                                                         | 17     |

| 3.3                               | Service de GitLab Runner opérationnel                                                                                       | 18     |

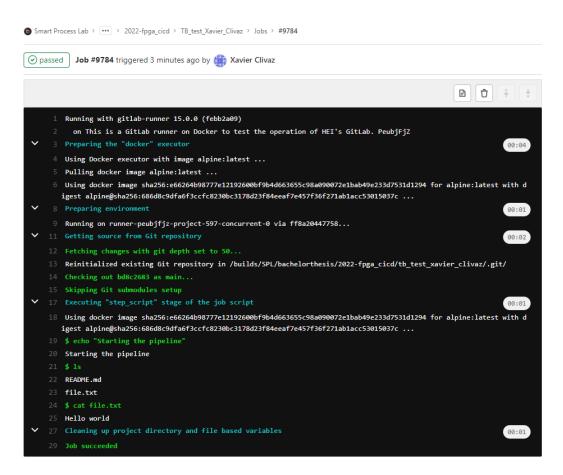

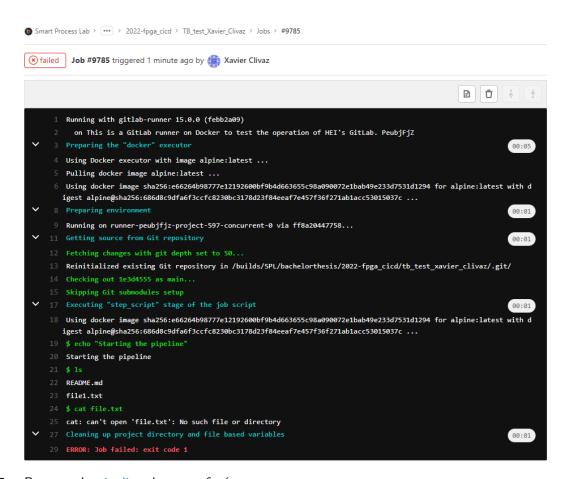

| 3.4                               | Passage du pipeline de test avec succès                                                                                     | 19     |

| 3.5                               | Passage du pipeline de test refusé                                                                                          | 20     |

| 3.6                               | Pipeline des processus de développement matériel                                                                            | 21     |

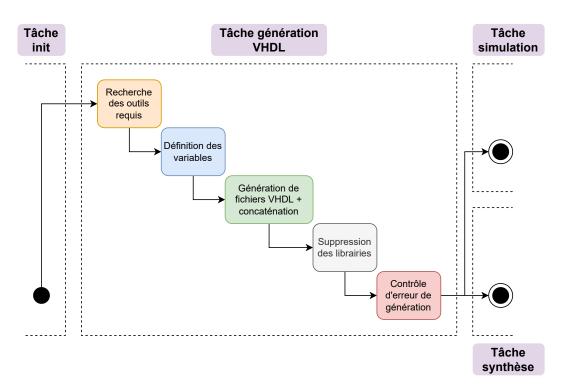

| 3.7                               | Vue d'ensemble du workflow génération VHDL                                                                                  | 22     |

| 3.8                               | Schéma fonctionnel du workflow génération VHDL                                                                              | 23     |

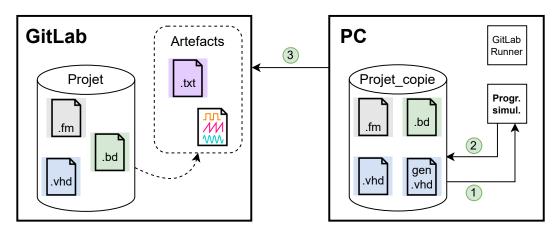

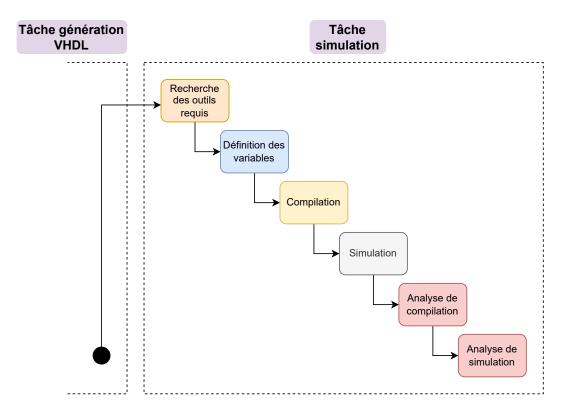

| 3.9                               | Vue d'ensemble du workflow simulation                                                                                       | 24     |

| 3.10                              | Schéma fonctionnel du workflow simulation                                                                                   | 25     |

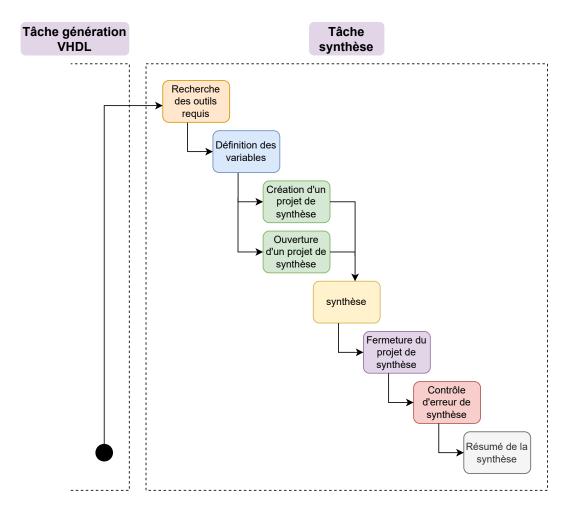

| 3.11                              | Vue d'ensemble du workflow synthèse                                                                                         | 26     |

| 3.12                              | Schéma fonctionnel du workflow synthèse                                                                                     | 27     |

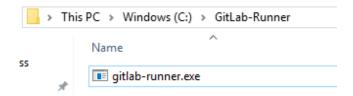

| 4.1                               | Préparation du fichier d'exécution de GitLab Runner                                                                         | 30     |

| 4.2                               | Enregistrement du service de GitLab Runner dans un référentiel partagé                                                      | 31     |

| 4.3                               | Changement du nom de l'exécutable <i>PowerShell</i> dans le fichier config.toml                                             | 31     |

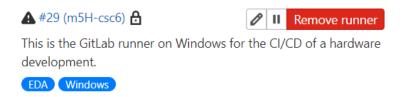

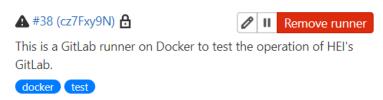

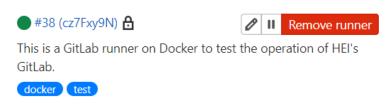

| 4.4                               | Vérification du service de GitLab Runner non opérationnel sur le référentiel partagé                                        | 32     |

| 4.5                               | Erreur de lancement du service de GitLab Runner                                                                             | 32     |

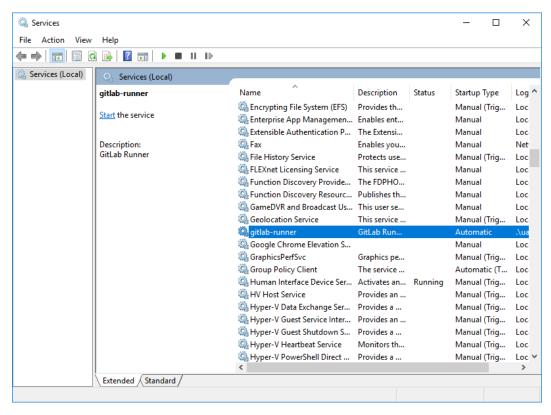

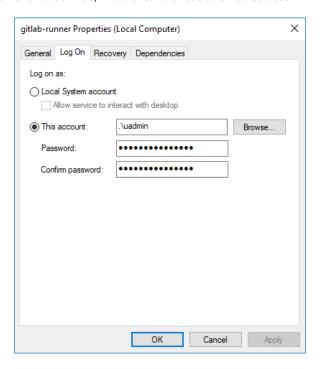

| 4.6                               | Fenêtre du gestionnaire de services Windows                                                                                 | 33     |

| 4.7                               | Fenêtre des propriétés utilisateurs du service de GitLab Runner                                                             | 33     |

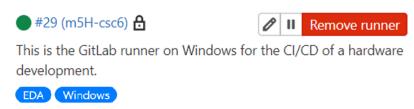

| 4.8                               | Vérification du service de GitLab Runner opérationnel sur le référentiel partagé                                            | 34     |

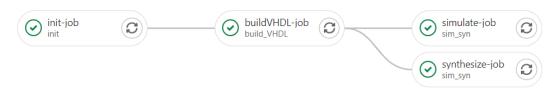

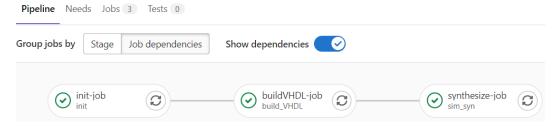

| 4.9                               | Etapes du pipeline                                                                                                          | 35     |

| 4.10                              | Illustration d'un sous-module                                                                                               | 38     |

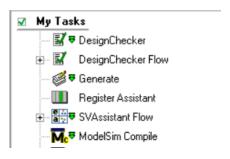

| 4.11                              | Exemple de tâches présentes dans le programme HDS                                                                           | 45     |

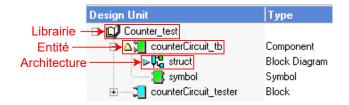

| 4.12                              | Exemple de librairie, d'entité et d'architecture dans un projet                                                             | 46     |

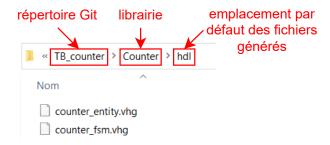

| 4.13                              | Emplacement des fichiers générés dans un exemple de projet                                                                  | 47     |

| 4.14                              | Emplacement du fichier concaténé dans un exemple de projet                                                                  | 48     |

| 4.15                              | Exemple d'affichage d'informations de la génération                                                                         | 48     |

| 5.1  | Projet chronomètre                                                        | 58 |

|------|---------------------------------------------------------------------------|----|

| 5.2  | Meilleur cas : tous les jobs sont activés                                 | 59 |

| 5.3  | Réussite du pipeline avec les quatre jobs                                 | 59 |

| 5.4  |                                                                           | 60 |

| 5.5  |                                                                           | 60 |

| 5.6  | Réussite de la génération VHDL avec la simulation et la synthèse activées | 61 |

| 5.7  | Exemple d'artefacts déposés après le job de synthèse                      | 61 |

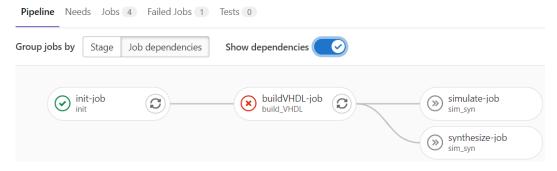

| 5.8  | Pire cas : erreur de génération VHDL                                      | 62 |

| 5.9  | Echec du pipeline à cause du job de génération VHDL                       | 62 |

| 5.10 | Pire cas : erreur de simulation                                           | 63 |

| 5.11 | Echec du pipeline à cause du job de simulation                            | 63 |

| 5.12 | Erreur de simulation                                                      | 64 |

| A.1  | Installation de l'image Docker préconfigurée                              | 69 |

| A.2  |                                                                           | 70 |

| A.3  |                                                                           | 71 |

| A.4  | GitLab Runner opérationnel                                                | 71 |

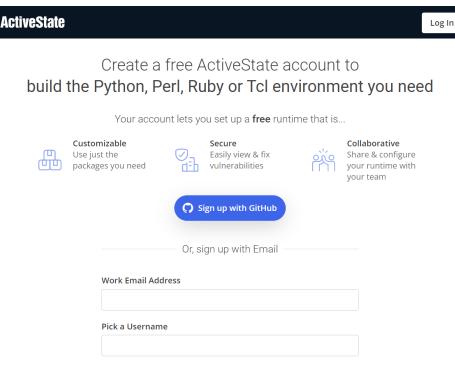

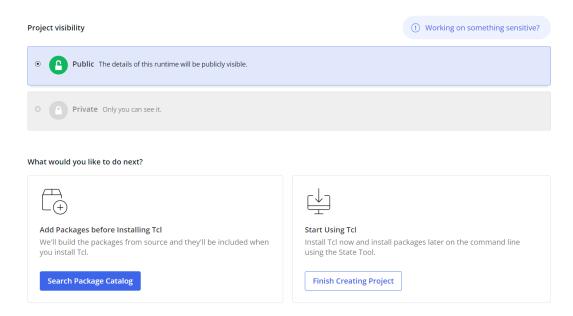

| B.1  | Création d'un compte ActiveState                                          | 73 |

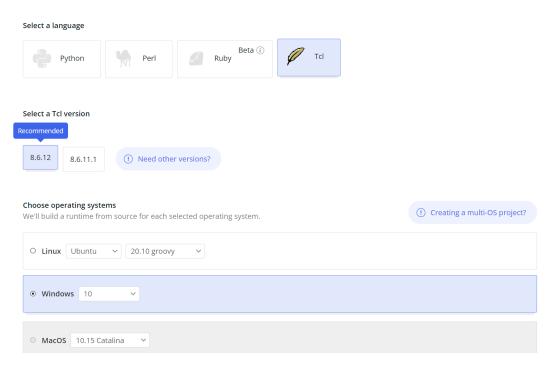

| B.2  | Sélection du porgamme et des paramètres                                   | 74 |

| B.3  | Sélection de la suite des paramètres                                      | 74 |

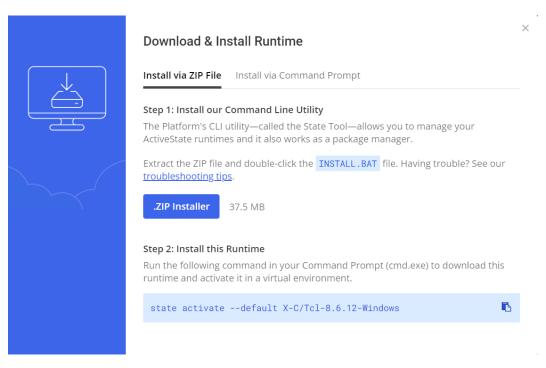

| B.4  |                                                                           | 75 |

| B.5  |                                                                           | 75 |

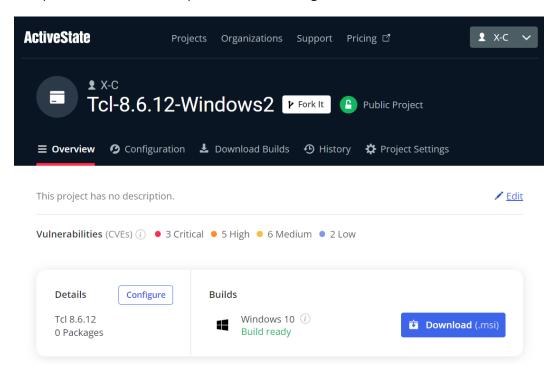

| B.6  |                                                                           | 76 |

| B.7  | 31                                                                        | 76 |

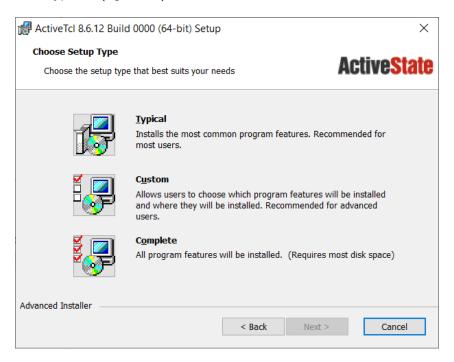

| B.8  | 1                                                                         | 77 |

| B.9  | Installation terminée                                                     | 77 |

| C.1  | 1 3                                                                       | 79 |

| C.2  | 9 1                                                                       | 79 |

| C.3  | 3                                                                         | 80 |

| C.4  |                                                                           | 80 |

| C.5  |                                                                           | 81 |

| C.6  | Vérification du sous-module inclus dans le dépôt "Projet" sur GitLab 8    | 81 |

|      |                                                                           |    |

|      |                                                                           |    |

## Liste des tableaux

| 2.1 | Comparatif des différents outils C | Ι. |  |  |  |  |  |  |  |  |  | 8 |

|-----|------------------------------------|----|--|--|--|--|--|--|--|--|--|---|

## Liste des codes sources

| 3.1          | Configuration du fichier .gitlab-ci.yml                                                | 18       |

|--------------|----------------------------------------------------------------------------------------|----------|

| 4.1          | Script : .gitlab-ci.yml, structure incomplète                                          | 36       |

| 4.2          | Script : .gitlab-ci.yml, partie : job d'initialisation                                 | 37       |

| 4.3          | Script : .gitlab-ci.yml, partie : job de génération VHDL                               | 39       |

| 4.4          | Script : .gitlab-ci.yml, partie : job de simulation                                    | 40       |

| 4.5          | Script : .gitlab-ci.yml, partie : job de synthèse                                      | 41       |

| 4.6          | Script : .gitlab-ci.yml, partie : variables d'environnement globales                   | 42       |

| 4.7          | Script : GenVHDL_Workflow_main.tcl, partie : outils requis                             | 43       |

| 4.8          | Script: searchPaths.tcl, partie: recherche HDS                                         | 44       |

| 4.9          | Script : GenVHDL_Workflow_main.tcl, partie : variables d'environnement                 | 44       |

| 4.10         | Script : GenVHDL_Workflow_main.tcl, partie : lancement d'HDS en mode shell             | 46       |

| 4.11         | Script : GenVHDL_Workflow_HDS.tcl, partie : configuration de la génération VHDL        | 46       |

| 4.12         | Script : GenVHDL_Workflow_HDS.tcl, partie : génération de fichiers VHDL                | 46       |

| 4.13         | Script : GenVHDL_Workflow_HDS.tcl, partie : concaténation des fichiers                 |          |

| 4.14         | VHDL                                                                                   | 47       |

| 4.14         | Script : GenVHDL_Workflow_main.tcl, partie : suppression des importations de librairie | 48       |

| 4.15         | Script : checkErrors.tcl, partie : HDL Designer Series                                 | 40       |

| 4.15         | Script : Sim_Workflow_main.tcl, partie : outils requis                                 | 49       |

| 4.10         | Script : Sim_Workflow_ModelSim.tcl, partie : création de la librairie de               | 49       |

| 4.17         | simulation                                                                             | 50       |

| 4.18         |                                                                                        | 50       |

| 4.10         | Script : Sim_Workflow_ModelSim.tcl, partie : compilation                               | 51       |

| 4.19         | Script: Sim_vvorknow_wodelSim.tci, partie: Simulation                                  | 51       |

| 4.20         | Script: Syn_Workflow_main.tcl, partie: outils requis                                   | 51       |

| 4.21         | Script: Syn_Workflow_main.tcl, partie: lancement d'ISE en mode shell                   | 52<br>52 |

| 4.22         |                                                                                        | 52<br>53 |

| 4.23         | Script : project_name.xise, exemple de projet ISE                                      | 53<br>53 |

|              | Script : Syn_Workflow_ISE.tcl, partie : ouverture d'un projet ISE                      |          |

| 4.25         | Script : Syn_Workflow_ISE.tcl, partie : création d'un projet ISE                       | 54       |

| 4.26         | Script : Syn_Workflow_ISE.tcl, partie : sauvegarde des propriétés des pro-             | E 4      |

| 4.07         | Cessus                                                                                 | 54       |

| 4.27<br>4.28 | Script : Syn_Workflow_ISE.tcl, partie : processus de synthèse                          | 55<br>55 |

| 5.1          | Script : Sim Workflow main.tcl. partie : outils requis                                 | 65       |

## 1 Introduction

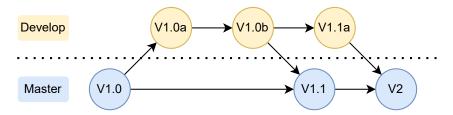

Ancrée dans l'esprit des développeurs, la gestion de versions ne se présente plus. Cette technique favorise le suivi et la maintenance des changements apportés au code d'un développement logiciel. Elle a l'avantage de garder un historique complet des modifications et de faciliter grandement le travail collaboratif sur un même projet.

Figure 1.1 Exemple de gestion de versions avec deux branches

Effectivement, la figure 1.1 se compose de plusieurs versions ainsi que de branches différentes. Bien évidemment qu'il pourrait y avoir plus de branches pour que chaque développeur en possède une à lui seul. Cela permettrait de travailler chacun sur une part du projet sans qu'un conflit n'entre en jeu au sein des collaborateurs. Lorsqu'une partie est terminée, une version est alors créée. Si dans un futur proche, un problème venait à être perçu par un employé ou même un client, revenir à une version antérieure est tout à fait envisageable.

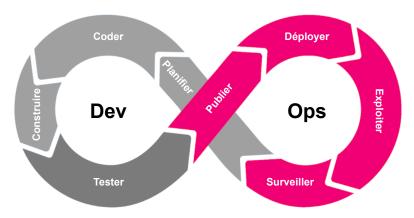

Figure 1.2 Méthode DevOps

D'autres méthodes viennent compléter la gestion de versions telle que le DevOps (figure 1.2). Celle-ci vise à automatiser les processus d'un développement logiciel entre les équipes de développement (partie grise de la figure 1.2) et les équipes d'exploitation (partie rose de la figure 1.2) pour renforcer la collaboration. Elle a donc élaboré l'intégration continue (Continuous Integration) (CI) et la distribution continue (Continuous Delivery) (CD) qui sont devenues les moyens de prédilection envers les développeurs. Ils permettent l'automatisation de plusieurs processus lors de chaque nouvelle version. Ces outils consistent généralement à construire, tester et déployer une conception logicielle (figure 1.5). La motivation de cette invention découle du gain de temps entre le lancement d'un projet et la commercialisation de celui-ci, exprimé en anglais par

"time to market". Effectivement, les machines sont en constante évolution alors que les êtres humains sont limités physiquement et moralement. De nombreux autres avantages peuvent être mentionnés tels que la collaboration en équipe, un débogage plus facile, une réduction des coûts, ainsi que la qualité et bien d'autres.

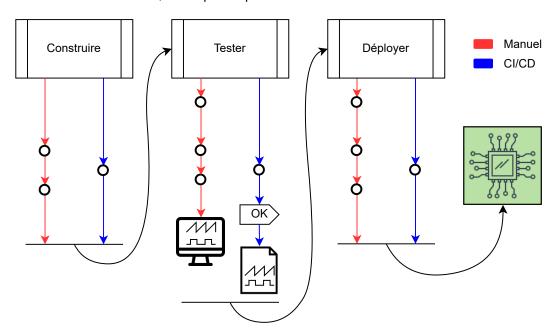

Figure 1.3 Illustration d'une automatisation de plusieurs processus

La figure 1.5 illustre parfaitement la distinction entre le monde manuel (flèches rouges) et le monde du CI/CD (flèches bleues) des processus. Les tâches de construction et de déploiement demandent nettement moins d'actions pour s'exécuter entièrement. La phase de test est un peu différente. Le résultat est généralement validé visuellement par le développeur à l'aide de comportements physiques ou virtuels. Le CI va valider lui-même les comportements en insérant des tests. Il va répondre par une réponse totale, soit oui, soit non, pour passer au déploiement. Un fichier contenant les résulats peut toujours être créé. Selon la réussite de tous les processus, le logiciel est transféré directement vers la carte électronique afin que'elle soit programmée et fonctionnelle. Le tuyau dans lequel cheminent toutes ces tâches s'appelle un pipeline.

La Haute Ecole d'Ingénierie (HEI) fait partie intégrante des universités et entreprises travaillant avec ces moyens d'aujourd'hui. Elle met en place ce système pour des projets qui concernent le développement de produits logiciels.

### 1.1 Problématique

La HEI étant une université en même temps qu'une entreprise, elle traite une large gamme de spécialisations dans le domaine de l'industrie. Ayant observé l'optimisation de ces pratiques sur des développements logiciels, elle souhaite à présent mettre en oeuvre un système de processus automatisé consacré au développement matériel. Il s'agit d'un développement où l'on programme un circuit intégré à partir d'un langage de description

matériel (Hardware Description Language) (HDL) (figure 1.4). L'inexistance réside dans le fait que le CI pour ces développements est peu connu et faiblement exploité dans l'industrie.

Figure 1.4 Carte de développement FPGA, FPGA-EBS

Il s'agit véritablement d'une problématique puisque ces conceptions matérielles sont tout aussi complexes que celles logicielles. Effectivement, aussitôt qu'un produit comporte plusieurs parties distinctes, la difficulté de les associer s'accroît diligemment. Sans ces outils CI, les parties sont généralement testées séparement, ce qui ne garantit en rien le fonctionnement global. Il vaut mieux procéder à des tests regroupant tous ces blocs simultanément.

Les principaux acteurs touchés sont les développeurs. Ils ne permettent pas de garantir la qualité du produit sans devoir passer un nombre inconsidérable d'heures supplémentaires au développement. Les clients sont aussi atteints en raison de leur position en bout de chaîne de production. Tous les retards accumulés leurs sont répercutés au déploiement. Il ne s'agit donc pas d'un avantage concurrentiel.

### 1.2 Objectifs

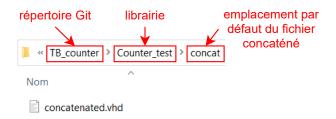

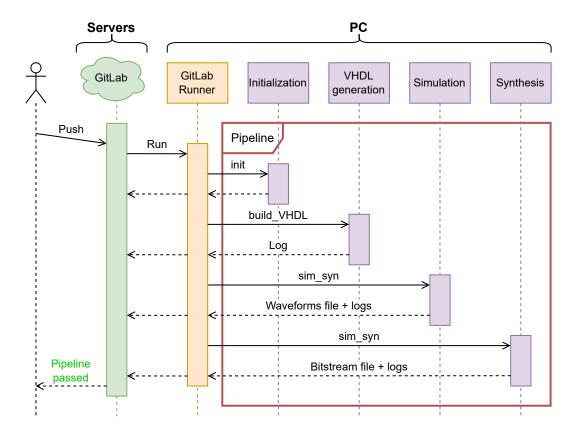

Figure 1.5 Pipeline automatisé avec la plateforme GitLab [1]

Le but premier de ce travail est d'implémenter un pipeline automatisé pour un développement matériel, plus particulièrement pour un module de développement FPGA (figure 1.4). Ce pipeline doit être adapté sur la plateforme d'hébergement GitLab [1] établie dans les serveurs de la HEI. L'outil de GitLab s'occupant de l'exécution des processus, appelé GitLab Runner [2], doit être installé sur une machine physique afin d'éviter l'installation de tous les programmes de conception à chaque lancement du pipeline. Il est demandé de concevoir plusieurs flux de travail. Premièrement, une génération du code source en VHDL doit être faite à partir du programme HDL Designer Series (HDS). En suivant, une simulation ainsi qu'une analyse doivent être élaborées. En dernier lieu, il reste la synthèse. Elle s'occupe de générer le fichier de configuration, appelé bitstream, pour un réseau de portes programmables sur site (Field-Programmable Gate Array) (FPGA) du fabricant Xilinx [3], prêt à être déployé sur le module de développement. Il est aussi demandé de gérer l'utilisation des différents flux de travail qu'en cas de nécessité. A savoir que l'utilisateur est libre de lancer une simulation et/ou une synthèse à chaque nouvelle version du projet.

#### 1.3 Méthodologie de recherche

La méthodologie de recherche utilisée dans cette thèse consiste tout d'abord à dresser un état de l'art sur les outils de développement matériel utilisés au sein du CI/CD. Une fois la recherche scientifique terminée, une vue d'ensemble de toute l'automatisation du pipeline sera réalisée dans le but d'implémenter le tout plus facilement. Un choix des programmes utilisés sera aussi effectué. En parallèle, l'implémentation sera élaborée. Une validation des résultats sera faite lorsque l'implémentation sera terminée.

### 1.4 Structure du rapport

Le chapitre 2 (Analyse) contient plusieurs définitions et l'état de l'art. Il s'agit de définitions de termes importants qui constituent le projet. L'état de l'art concerne les outils actuels pour le développement matériel intégrés dans le Cl.

Le chapitre 3 (Conception) contient la vue d'ensemble de l'implémentation ainsi que le choix des outils observés.

Le chapitre 4 (Implémentation) contient la mise en oeuvre de l'outil d'intégration continue (Continuous Integration) en plus des flux de travail pour réaliser les objectifs visés.

Le chapitre 5 (Validation) contient l'analyse des résultats de l'implémentation et la validation de ceux-ci.

Le chapitre 6 (Conclusion) conclue la thèse en donnant l'état actuel de la recherche, les problèmes rencontrés ainsi que les étapes futures.

## 2 | Analyse

L'analyse permet tout d'abord d'expliquer les concepts fondamentaux qui sont travaillés tout au long du projet. Par après, un état de l'art est dressé sur les différents outils existants pour l'intégration et la livraison continue en ce qui concerne le développement matériel.

#### Table des matières

| 2.1 | Définitions                                      |

|-----|--------------------------------------------------|

|     | 2.1.1 FPGA                                       |

|     | 2.1.2 Intégration continue et livraison continue |

|     | 2.1.3 Référentiel partagé                        |

| 2.2 | CI/CD pour développement matériel                |

| 2.3 | Outils de CI                                     |

| 2.4 | Génération de fichiers VHDL à partir de HDS      |

| 2.5 | Simulation                                       |

|     | 2.5.1 Tests                                      |

|     | 2.5.2 Simulateurs                                |

|     | 2.5.3 Compléments                                |

| 2.6 | Synthèse et implémentation                       |

#### 2.1 Définitions

#### 2.1.1 FPGA

FPGA est l'acronyme de réseau de portes programmables sur site (Field-Programmable Gate Array). Il s'agit d'un circuit intégré pouvant être programmable de manière matérielle autant de fois que nécessaire après sa fabrication. Il est composé d'un nombre incalculable de portes. Un HDL spécifique permet de câbler ces portes (VHSIC-HDL, Very High Speed Integrated Circuit Hardware Description Language (VHDL) dans le cadre de ce travail).

#### 2.1.2 Intégration continue et livraison continue

Plongé actuellement dans l'industrie 4.0, l'efficacité pour tout développement logiciel doit être de mise. Les développeurs ne souhaitent plus perdre leur temps sur des tâches chronophages telles que les phases de test de leurs développements. Les utilisateurs, quant à eux, restreignent de plus en plus leur délai pour obtenir l'application qu'ils désirent. C'est ainsi que des méthodes doivent permettre de répondre à ces inombrables contraintes. Il existe une pratique de plus en plus sollicitée qui se nomme le DevOps. Le DevOps se construit à partir d'un pipeline d'intégration continue (Continuous Integration) (CI) et de distribution continue (Continuous Delivery) (CD). Il s'agit d'une manière d'automatiser une grande partie des workflows (figure 1.2). L'idée est de remplacer certaines tâches des développeurs (partie grisée de la figure 1.2) ainsi que des opérateurs (partie rosée de la figure 1.2) pour rendre le tout avantageux.

Le CI, qui concerne les développeurs, assure continuellement le fonctionnement global du programme après chaque modification apportée. Un projet logiciel comporte bien souvent de nombreuses parties qui rendent le tout complexe. Pour que plusieurs développeurs puissent travailler sur des parties distinctes, un processus de construction ainsi que de test sont lancés pour garantir qu'aucun conflit ne soit présent. Seulement par après, les modifications sont fusionnées avec le programme sur un référentiel partagé qui se situe sur une plateforme d'hébergement.

La CD, parfois similaire au déploiement continu, est le processus qui publie les mises à jour fusionnées sur le référentiel partagé. Ce référentiel est l'endroit visible par les opérateurs qui vont pouvoir procéder par la suite au déploiement du programme manuellement. Le déploiement continu est le déploiement du programme mais de manière automatique. Il s'agit de la phase de transfert de la mise à jour depuis le référentiel vers l'utilisateur.

Un pipeline CI/CD améliore considérablement la collaboration de plusieurs développeurs au sein du même projet. Elle optimise également la vitesse de développement et garantit la fiabilité et la qualité du logiciel. La communication entre la partie développement et opération est nettement plus rapide. Les clients obtiendront donc leur application dans un délai bien plus court pour bénéficier d'un avantage concurrentiel. Ils pourront aussitôt donner des informations sur l'utilisation du logiciel directement aux développeurs pour qu'ils recommencent leur cycle de mise à jour.

#### 2.1.3 Référentiel partagé

Dans le milieu du développement logiciel et matériel, un référentiel partagé désigne un répertoire sur une plateforme d'hébergement permettant le développement collaboratif (GitLab [1] dans le cadre de ce travail). Il stocke les fichiers bruts et en fait différentes versions en fonction de chaque modification apportée. Un système de branche peut aussi être possible afin de travailler chacun sur une branche distincte pour éviter tout conflit. Généralement tous les hébergeurs rendent leur plateforme compatible au DevOps.

#### 2.2 CI/CD pour développement matériel

Il faut tout d'abord bien comprendre la procédure de programmation d'un développement matériel pour un FPGA. Un chemin d'étapes est représenté à la figure 2.1. Il est indispensable de générer au départ un code VHDL. Un processus de synthèse s'en suit pour créer une netlist qui décrit le circuit électronique. Le placement et le routage, appelés implémentation, sont les phases qui suivent afin de positionner les composants du schéma dans la structure d'un FPGA et établir la liaison entre chaque composant. Ceci est sauvé dans un fichier bitstream. Pour terminer, il suffit de programmer la carte.

Figure 2.1 Chemin de programmation d'une carte FPGA

La figure 2.1 montre parfaitement qu'un développement matériel traverse différentes étapes tout comme un développement logiciel. Le développement matériel peut donc très bien passer par un pipeline automatisé. Les outils nécessaires vont quant à eux différer de ceux d'un développement logiciel.

Pour donner une idée concrète, il suffit de prendre l'exemple d'un circuit à développer pour une carte FPGA. Plusieurs développeurs collaborent sur ce même projet. Ils amènent chacun des modifications qu'ils vont ensuite vouloir centraliser sur un référentiel. Lors de chaque poussée, avant d'adjoindre ces mises à jour, la génération des fichiers en code VHDL va être effectuée (partie construction de la figure 1.2). Seulement par après, une simulation peut être lancée depuis un banc de test pour vérifier le bon fonctionnement dans son ensemble (partie test de la figure 1.2). Si ceci est en ordre, la fusion des mises à jour peut être faite. La suite des opérations concerne le CD. Afin de rendre prêt l'opérateur à programmer la carte, il est primordial de synthétiser le code VHDL et l'implémenter en un fichier bitstream propre au fabricant de la carte FPGA (partie publication de la figure 1.2).

#### 2.3 Outils de Cl

Cette analyse sur les outils d'intégration continue (Continuous Integration) est tirée d'un ancien travail de diplôme [4].

Plusieurs outils sont existants pour l'exécution des différents workflows d'un pipeline. Une liste non exhaustive est présente ci-dessous. Elle regroupe les noms les plus connus :

— Gitlab-CI [5]

- Jenkins [6]

- Bitbucket Pipelines [7]

- Travis CI [8]

Une analyse de ces différents outils a été réalisée uniquement avec des cas d'utilisation gratuits.

| Caractéristiques                                       | Git <sub>L</sub> ab-CI                           | Jenkins                                  | Bitbucket.<br>Pipelines               | Travis CI     |

|--------------------------------------------------------|--------------------------------------------------|------------------------------------------|---------------------------------------|---------------|

| Dédier une machine physique comme exécuteur            | oui                                              | oui                                      | oui                                   | non           |

| Possibilité de liaison avec Gitlab                     | oui                                              | oui                                      | non                                   | oui           |

| Temps disponible par mois pour le CI                   | 400 min pour<br>runner de<br>GitLab              | pas de limite                            | 50 min pour<br>runner de<br>Bitbucket | pas de limite |

| Espace mémoire pour les artefacts                      | configurable /<br>temps de garde<br>configurable | Espace de la<br>machine à<br>disposition | 1GB                                   | aucun         |

| Possibilité d'effectuer plusieurs tâches simultanément | oui                                              | oui                                      | oui                                   | oui           |

| Informe en temps réel les étapes du Cl                 | oui                                              | oui                                      | oui                                   | oui           |

Table 2.1 Comparatif des différents outils Cl

GitLab-CI est l'outil le plus favorable dans le cadre de ce travail. La plateforme d'hébergement utilisée étant GitLab [1], il s'agit de son propre outil. De plus, il est déjà exploité dans d'autres projets de la HEI. GitLab-CI peut être auto-hébergé sur une machine physique à l'aide d'un petit logiciel lié aux serveurs de GitLab appelé GitLab Runner [2]. Un runner (GitLab Runner dans ce cas) est un programme qui exécute toutes les commandes implémentées dans le pipeline. De plus, sa durée d'utilisation pour le CI devient illimitée. Il est tout à fait possible de sauver tous les fichiers qui contiennent les informations de chaque étape du pipeline. Ces fichiers s'appelent des artefacts.

Jenkins est aussi un outil qui aurait pu être employé. Un runner existe pour être autohébergé sur une machine physique. Il est compatible avec la plateforme GitLab [1] et offre un espace considérable pour les artefacts. Il est cependant plus difficile à configurer et donc moins intuitif.

Bitbucket Pipelines est beaucoup plus restreint. Il ne permet pas la liaison avec la plateforme utilisée. Il est aussi limité par le stockage maximal des archives d'artefacts.

Tout aussi contraignant, Travis CI ne possède pas de runner pour une machine physique. Il n'est d'ailleurs pas possible de sauver les informations des différentes étapes.

Il est à noter que toutes les informations ont été mises à jour au mois de juin 2022.

### 2.4 Génération de fichiers VHDL à partir de HDS

Cette partie concernant la génération de fichiers VHDL est spécifique à l'environnement HDL Designer Series [9]. Il prend en charge le langage HDL pour la conception d'FPGA. Il est possible d'implémenter le design sous différents aspects tels que par une machine

d'état, des diagrammes en bloc ou encore directement dans le langage HDL (figure 2.2). A la fin de la conception, le passage par un langage HDL est obligatoire pour pouvoir par la suite synthétiser et programmer la carte FPGA.

Le logiciel HDS a la possibilité de convertir tous ces types d'implémentation directement en lignes de commande. Il s'agit d'un langage de script Tool Command Language (Tcl) qui remplace l'interface graphique. Toute une documentation [10] sur les commandes Tcl est fournie. Ceci est un avantage majeur puisque le Cl exécute ses tâches uniquement par des lignes de commande.

Figure 2.2 Arborescence des conversions pour la génération VHDL

#### 2.5 Simulation

L'article scientifique [11] explique que cette étape de simulation dans un pipeline est spécifiquement importante car elle permet d'exécuter les tests dans un milieu déterministe invariant dans le temps et elle contribue beaucoup à la reproductibilité des résultats. Afin de maximiser les avantages qu'un tel développement puisse offrir, indiquer clairement les moyens et l'environnement de test exploités est capital. Les développeurs ne sont absolument pas certains que les résultats n'aient pas été affectés de manière involontaire lorsqu'ils lancent leurs exécutions manuellement sur leur propre machine. Effectivement, différentes versions d'outils peuvent exister tout comme des changements locaux sur leur machine.

#### 2.5.1 Tests

La thèse [12] démontre l'utilisation de plusieurs outils pour cette étape de simulation. Elle dit utiliser un outil spécialement pour les tests unitaires appelé VUnit [13] et un banc de test pour les tests globaux appelé cocotb [14]. VUnit et cocotb sont des programmes permettant de mettre en oeuvre les tests avec le langage Python. L'auteur Alberto Martínez Cuesta [12] explique que ces outils ont été créés dans le but de ne pas utiliser des

langages de description matériels relativement compliqués, qui sont développés spécifiquement pour la conception et non pour les tests. La conception et la simulation doivent être traitées avec des démarches distinctes puisque ce sont des problèmes différents. La construction de tests est simplifiée par l'utilisation d'un outil logiciel qui est un langage de très haut niveau.

La documentation VUnit [13] explique que ce logiciel ne fait que compléter les méthodologies de test traditionnelles en favorisant l'approche de tester tôt et souvent. Il n'est donc pas possible de remplacer en totalité les tests avec ce programme. La vérification qu'offre celui-ci réduit donc la charge des tests en prenant en charge la détection automatique des bancs de test. L'avantage de VUnit [13] est qu'il peut être utilisé n'importe où dans la phase de test, autant au début qu'à la fin.

La documentation cocotb [14] dit que son nom signifie "COroutine based COsimulation TestBench". Il est spécifié qu'il requiert un simulateur pour simuler la conception HDL peu importe le système d'exploitation. Un de ses avantages est qu'il contient un support pour le CI. Il a spécifiquement été conçu pour réduire les charges générales de test. La documentation donne plusieurs atouts de programmer en Python. L'écriture de ce langage est rapide. Il est facile de coder d'autres langages par le biais de celui-ci. Python dispose de beaucoup de librairies. Il est aussi très populaire.

L'outil HDS n'est malheureusement pas très connu par les scientifiques au niveau de la simulation. Pourtant, dans sa documentation [15], Mentor Graphics explique posséder un assistant permettant d'automatiser le processus de vérification et de test des conceptions en utilisant les nouvelles techniques, la méthodologie de vérification universelle (Universal Verification Methodology) (UVM) et la méthodologie de vérification ouverte (Open Verification Methodology) (OVM). Il dit aussi être capable de créer facilement des bancs de test UVM/OVM professionnels.

Un bref résumé de ces trois outils est présenté ci-dessous.

#### VUnit:

- Langage de test : Python

- Langage hardware: VHDL, SystemVerilog

- Systèmes d'exploitation supportés : Windows, Linux, macOS

- Spécialisation : spécifique aux tests unitaires du système

- Gratuit et open source

#### cocotb:

- Langage de test : Python

- Langage hardware : VHDL, SystemVerilog

- Systèmes d'exploitation supportés : Windows, Linux, macOS

- Spécialisation : banc de test pour des tests globaux du système

- Gratuit et open source

#### HDS:

- Langage de test : VHDL, SystemVerilog

- Langage hardware : VHDL, SystemVerilog

- Systèmes d'exploitation supportés : Windows, Linux

- Spécialisation : banc de test pour des tests globaux du système

- Payant avec une licence

#### 2.5.2 Simulateurs

Pour exécuter les tests, différents simulateurs sont employés tels que GHDL [16], un outil totalement open source, ou encore ModelSim [17]. Le projet [18] basé sur FPGA a décidé d'utiliser ce premier simulateur en partie puisqu'il est plus adapté à l'intégration continue et de part sa gratuité, il n'y a aucun soucis de l'exécuter dans un nuage (ex : Docker). Martin Jeřábek [19] ajoute aussi que la vitesse de simulation de GHDL [16] est plus performante par rapport au second logiciel et qu'il ne peut pas y avoir de problème de licence. Il est en revanche uniquement valable pour le langage VHDL. Contrairement à l'outil ModelSim [17], aussi très populaire, il est commercial. Il est relativement lourd mais permet aussi la visualisation graphique des signaux générés. Il est valable pour le langage VHDL ainsi que Verilog. Il est a souligner que uniquement ModelSim [17] offre la possibilité d'afficher les signaux de manière graphique. La documentation officielle de GHDL [16] affirme ne pas avoir de visualisateur et que ce logiciel génère uniquement des fichiers qui peuvent être de type VCD, FST ou encore GHW. Néanmoins, Il existe un outil de visualisation, nommé GTKWave [20], compatible selon la documentation GHDL [16]. L'article [21] a pu tester cette combinaison avec succès. Ces scientifiques ont dressé un organigramme (figure 2.3) montrant la procédure générale en plus de leurs commandes.

Figure 2.3 Organigrammes montrant la procédure générale de simulation (à gauche) et les commandes à utiliser à chaque étape (à droite).

Un bref résumé de ces deux outils est présenté ci-dessous.

#### GHDL:

- Gratuit et open source

- Langage hardware: VHDL

- Outils de test compatibles : VUnit, cocotb

- Systèmes d'exploitation supportés : Windows, Linux, macOS

- Visualisation graphique : non

- Traduction direct du langage VHDL en langage machine (gain de vitesse)

#### ModelSim:

- Payant avec une licence

- Langage hardware : VHDL, Verilog

- Outils de test compatibles : VUnit, cocotb

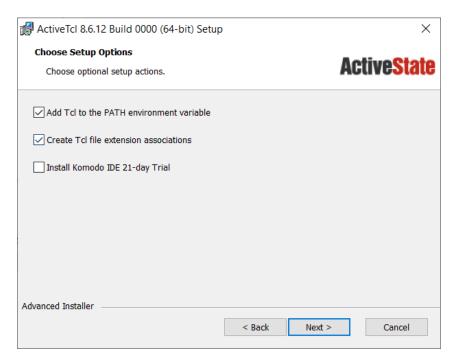

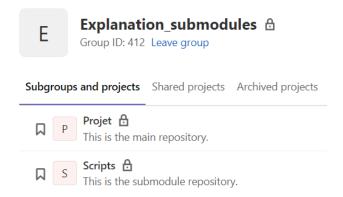

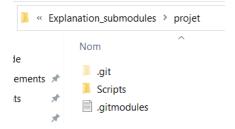

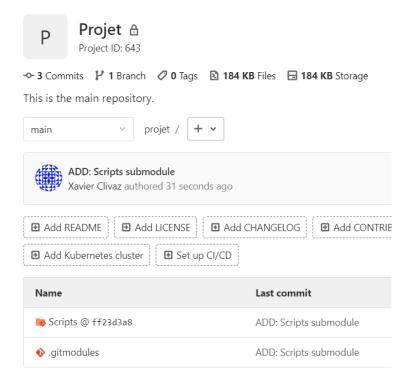

- Systèmes d'exploitation supportés : Windows, Linux